2024. 12. 16. 07:46

반응형

팹리스(Fabless)는 반도체 설계에만 집중하는 회사를 의미합니다. 즉, 반도체를 직접 생산하는 공장(Fabrication)이 없다는 뜻이죠.

팹리스가 하는 일

- 반도체 설계: 컴퓨터 칩, 스마트폰 프로세서 등 다양한 반도체 제품의 설계를 합니다. 이는 마치 건축가가 건물을 설계하는 것과 비슷합니다.

- 설계 도면 판매: 설계한 반도체 도면을 다른 회사에 판매하거나, 반도체 제조 공장(파운드리)에 위탁 생산을 의뢰합니다.

팹리스의 장점

- 빠른 시장 변화에 대한 대응: 대규모 투자가 필요한 생산 시설 없이 설계에만 집중할 수 있으므로, 빠르게 변화하는 시장에 유연하게 대응할 수 있습니다.

- 다양한 제품 개발: 다양한 종류의 반도체를 개발하여 제품 포트폴리오를 확장할 수 있습니다.

- 높은 수익성: 생산 시설 유지 비용이 들지 않아 높은 수익성을 확보할 수 있습니다.

팹리스의 단점

- 파운드리 의존도 높음: 반드 생산을 외부에 의존하기 때문에, 파운드리의 생산 능력이나 기술력에 영향을 받을 수 있습니다.

- 지식재산권 보호의 어려움: 설계 도면을 다른 회사에 제공해야 하므로, 지식재산권 침해의 위험에 노출될 수 있습니다.

대표적인 팹리스 기업

- 퀄컴: 스마트폰 프로세서

- 엔비디아: 그래픽 처리 장치(GPU)

- AMD: CPU, GPU

- 애플: 자체 프로세서 (A 시리즈)

왜 팹리스가 중요할까요?

- 반도체 산업의 다변화: 팹리스의 등장으로 반도체 산업은 설계와 생산이 분리되어 더욱 전문화되었습니다.

- 혁신 가속화: 팹리스는 새로운 아이디어를 빠르게 제품으로 구현하여 기술 혁신을 이끌고 있습니다.

- 다양한 제품 개발: 다양한 팹리스 기업들이 각자의 강점을 살려 다양한 종류의 반도체를 개발하고 있습니다.

결론적으로, 팹리스는 반도체 산업에서 핵심적인 역할을 담당하며, 끊임없는 기술 혁신을 통해 우리 삶을 변화시키는 데 기여하고 있습니다.

※ 참고)

팹리스의 설계와 VHDL, Verilog

네, 맞습니다. 팹리스에서 반도체를 설계할 때 주로 사용하는 언어가 **VHDL(Very High Speed Integrated Circuit Hardware Description Language)**와 Verilog입니다.

VHDL과 Verilog란?

VHDL과 Verilog는 하드웨어 기술설명 언어(HDL, Hardware Description Language)의 일종으로, 컴퓨터 칩과 같은 하드웨어를 설계하고 시뮬레이션하는 데 사용되는 고급 언어입니다. 마치 건축가가 건물 설계도를 그리는 것처럼, 팹리스 엔지니어는 VHDL이나 Verilog를 사용하여 반도체의 논리 회로를 상세하게 기술합니다.

- VHDL: 미국 국방성에서 개발되었으며, 엄격한 문법과 체계적인 구조를 가지고 있어 대규모 시스템 설계에 적합합니다.

- Verilog: 산업계에서 널리 사용되는 언어로, C언어와 유사한 문법을 가지고 있어 배우기 쉽고 생산성이 높습니다.

팹리스에서 VHDL/Verilog를 사용하는 이유

- 복잡한 회로의 정확한 표현: VHDL과 Verilog는 복잡한 논리 회로를 간결하고 명확하게 표현할 수 있습니다.

- 시뮬레이션을 통한 검증: 설계된 회로를 컴퓨터 상에서 시뮬레이션하여 오류를 사전에 발견하고 수정할 수 있습니다.

- 재사용 가능한 설계 모듈: 한번 설계한 모듈을 다른 설계에 재사용하여 개발 시간을 단축할 수 있습니다.

- 다양한 설계 도구와의 연동: VHDL과 Verilog는 다양한 설계 도구와 연동되어 효율적인 설계 환경을 제공합니다.

설계 과정 간략히 살펴보기

- Specification: 설계하고자 하는 반도체의 기능과 성능을 정의합니다.

- RTL Coding: VHDL 또는 Verilog를 사용하여 설계를 구체적인 코드로 작성합니다.

- Simulation: 작성된 코드를 시뮬레이션하여 설계의 동작을 검증합니다.

- Synthesis: HDL 코드를 실제 하드웨어에 매핑할 수 있는 논리 회로로 변환합니다.

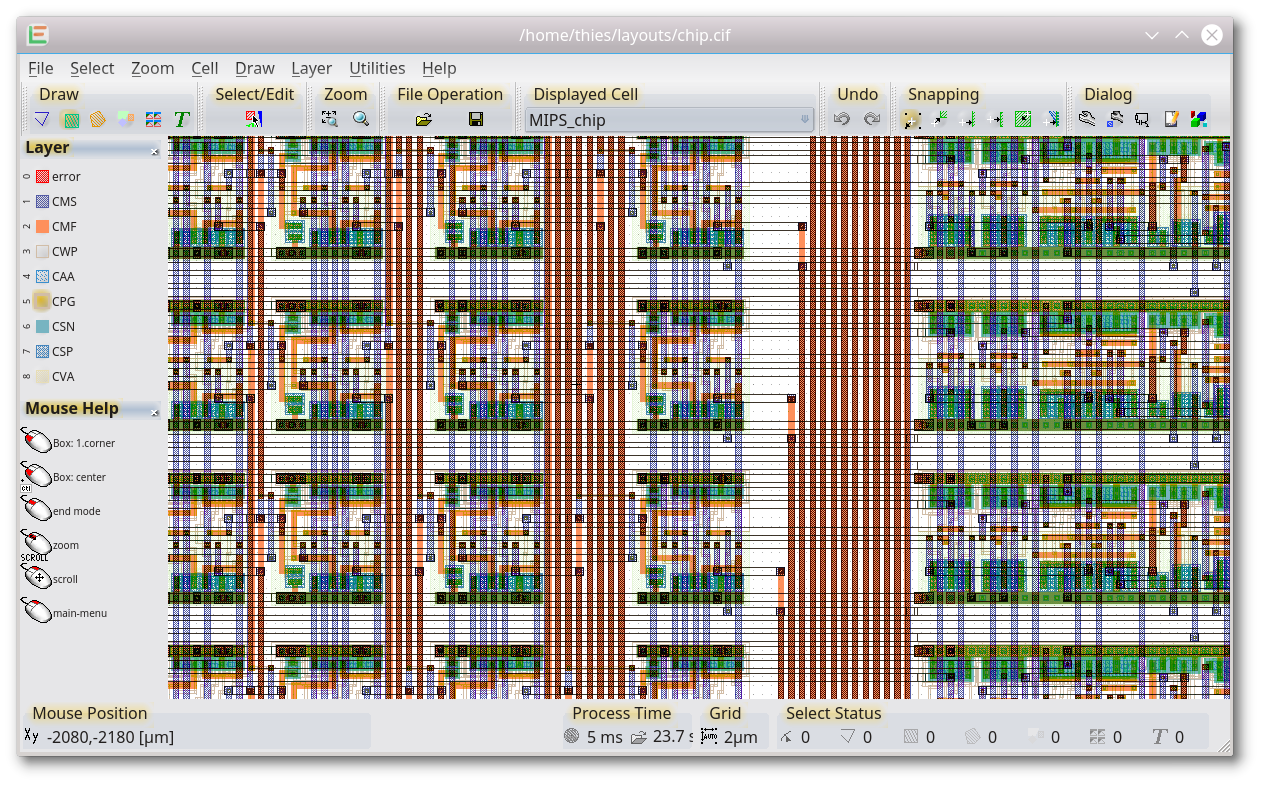

- Place & Route: 논리 회로를 실제 칩 위에 배치하고 연결합니다.

- Tape-out: 최종 설계 데이터를 파운드리에 전달하여 칩을 제작합니다.

반응형

'컴퓨터 잡다학메모' 카테고리의 다른 글

| 반도체 파운드리 (Foundry)에 대해 메모 (5) | 2024.12.16 |

|---|---|

| 반도체 디자인하우스에 대해 메모 (0) | 2024.12.16 |

| 반도체 소부장(소재, 부품, 장비)에 대해 메모 (1) | 2024.12.16 |

| 반도체에서 소부장-팹리스-디자인하우스-파운드리 각 과정 메모 (1) | 2024.12.16 |

| 프로세스와 쓰레드 (0) | 2024.12.11 |

콘텐츠 내 자동삽입광고